SSDs are made up of many individual memory cells that make up the operating principle of field-effect transistors as its own. To store the information, the gates of the transistors each have an additional, electrically insulated semiconductor layer, which acts as a charge trap (floating gate) and their state of charge – in the end so the stored information -. Be obtained even without a power supply for a long time

When connecting the memory cells all current SSDs use NAND architecture, in which the individual cells are connected in series. Furthermore, a distinction is made single-level memory cells (SLC) that store only one bit per cell multilevel memory cells (MLC) that can store two bits, and triple-level memory cells which can store three bits. TLCs therefore have a higher storage density than MLCs, which in turn are superior to the SLCs at this property.

limits of miniaturization

Like all electronic components have been and the memory cells of an SSD are getting smaller. Fraud in the early times of SSDs, the distance between the memory cells even 120 nm, shrank this measure over the years to 19 nm. However, the miniaturization has side effects. Thus, the likelihood that individual cells affect each other as the structures become smaller at the same rate. These interferences can at worst cause data inappropriate will be deleted or changed. In structures of today less than 20 nm, a critical limit is reached for “classical architectures”. Also for the production processes is difficult miniaturization. The photolithographic patterning process used meets the 10-nm range reaches its limits.

Photo: Samsung

Innovation overcomes limitations

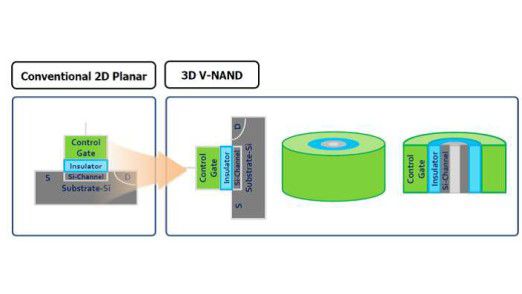

3D V-NAND shows a way out of the dilemma. In 3D V-NAND through an insulator made of silicon nitride (SiN), the floating gate, which consists of conventional planar structures of semiconductive polysilicon replaced. This keeps the charge after writing in charge traps laid (CTF: Charge Trap Flash) -. Even if the memory cell is no longer supplied with current

In addition to 3D V-NAND done a vertical arrangement of the CTF architecture , This leads to larger feature sizes, in turn, reduce the risk for interference between the memory cells. This V-NAND cells can be stacked vertically. Samsung T1, for example, has in its interior a three-dimensional flash memory with 32 layers.

Advantages of 3D V-NAND

-

High data density: With the vertical stacking of 32 layers is obtained as compared to conventional MLC flash memory is more than twice as high data density

-

High speed: Thanks to the reduced interference between the individual memory cells increases the programming speed of the cells

-

High durability:. The larger feature size allows more write cycles than conventional memory elements.

-

3D V-NAND technology

YouTube video to 3D V-NAND

No comments:

Post a Comment